C’est dans un communiqué de presse qu’Intel parle de sa technologie PowerVia. Et de ce que nous voyons ici, la technologie est intéressante puisqu’il ne s’agit que d’un aperçu de ce qu’il y a à venir. Concrètement, cette technologie permet à la fois d’augmenter la fréquence du processeur, mais aussi d’en baisser la tension.

Une évolution majeure dans la fabrication des puces

Ben Sell d’Intel explique comment la société a développé et prouvé la première solution d’alimentation arrière au monde, faisant ainsi un grand pas en avant dans la fabrication de puces.

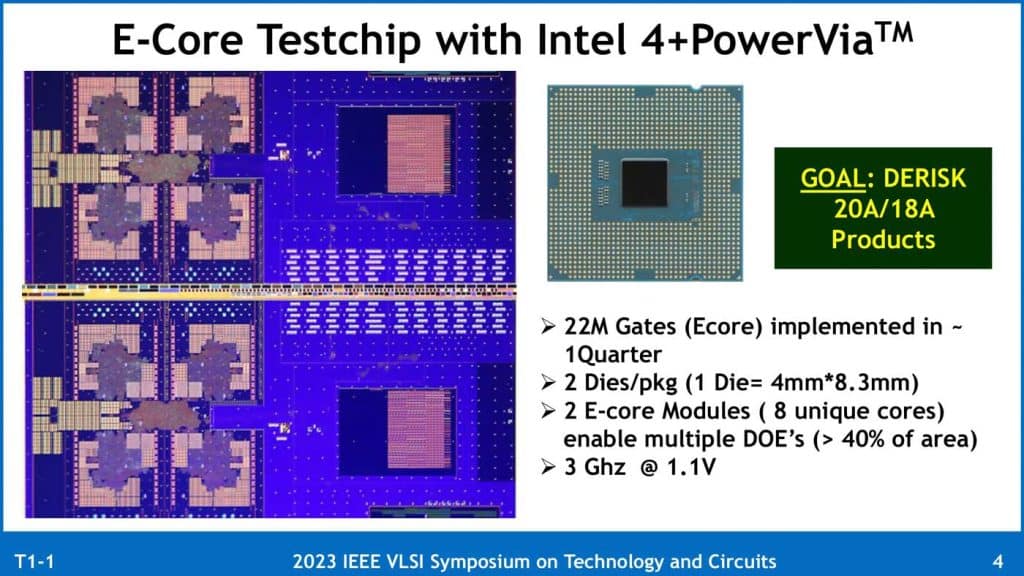

Intel est le premier du secteur à mettre en œuvre la fourniture d’alimentation par l’arrière sur une puce de test de type produit, atteignant les performances nécessaires pour propulser le monde dans la prochaine ère de l’informatique. PowerVia, qui sera introduit sur le nœud de processus Intel 20A au cours du premier semestre 2024, est la solution d’alimentation arrière d’Intel à la pointe de l’industrie. Il résout le problème croissant des goulots d’étranglement d’interconnexion dans la mise à l’échelle de la zone en déplaçant le routage de l’alimentation vers l’arrière d’une tranche.

« PowerVia est une étape majeure dans notre stratégie agressive de « cinq nœuds en quatre ans » et sur notre chemin pour atteindre un billion de transistors dans un boîtier en 2030. L’utilisation d’un nœud de processus d’essai et d’une puce de test ultérieure nous a permis de réduire les risques d’alimentation arrière pour nos principaux nœuds de processus, ce qui place Intel en tête de ses concurrents en ce qui concerne la mise sur le marché de la fourniture d’alimentation par l’arrière. »

–Ben Sell, vice-président du développement technologique d’Intel

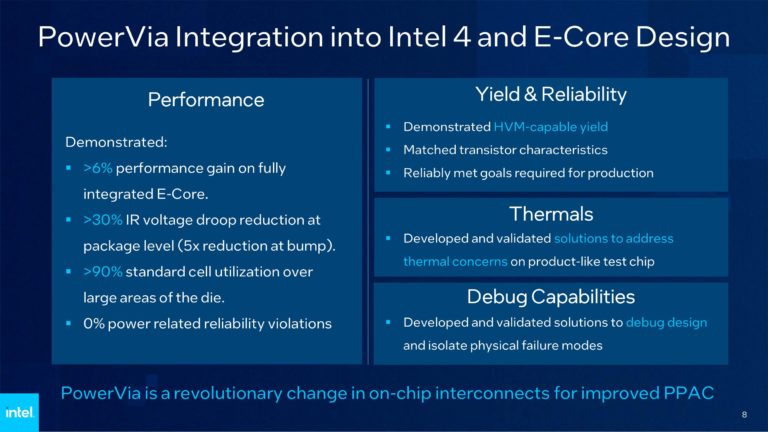

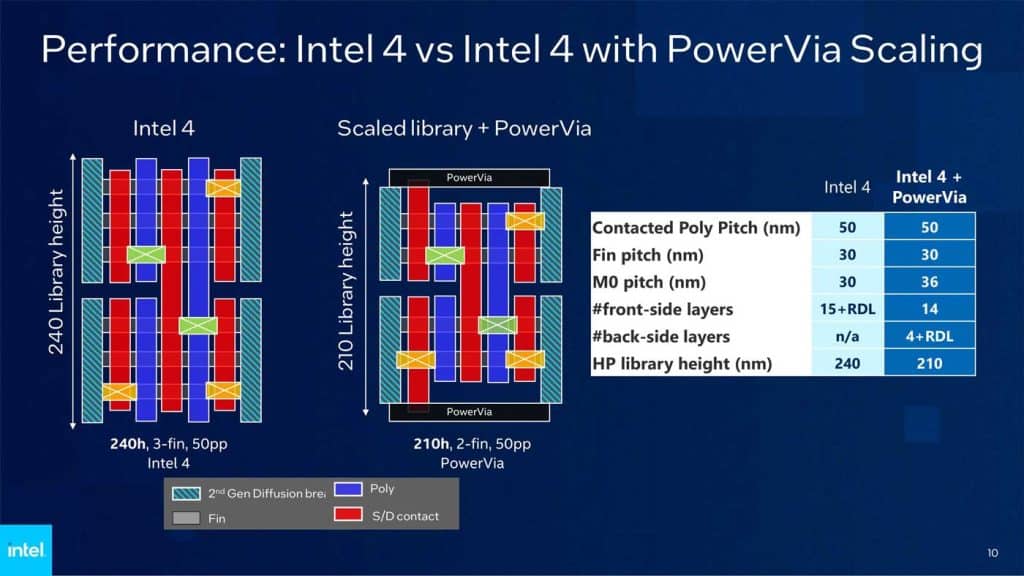

Comment ça marche : Intel a dissocié le développement de PowerVia du développement des transistors pour assurer sa préparation à la mise en œuvre du silicium basée sur les nœuds de processus Intel 20A et Intel 18A. PowerVia a été testé sur son propre nœud de test interne pour déboguer et garantir le bon fonctionnement de la technologie avant son intégration avec RibbonFET dans Intel 20A. Après la fabrication et les tests sur une puce de test en silicium, il a été confirmé que PowerVia apportait une utilisation remarquablement efficace des ressources de la puce avec une utilisation des cellules supérieure à 90 % et une mise à l’échelle majeure des transistors, permettant aux concepteurs de puces d’obtenir des gains de performances et d’efficacité dans leurs produits.

Intel présentera ces résultats dans deux articles lors du symposium VLSI du 11 au 16 juin à Kyoto, au Japon.

Pourquoi c’est important : PowerVia est bien en avance sur les solutions d’alimentation arrière de ses concurrents, offrant aux concepteurs de puces – y compris les clients Intel Foundry Services (IFS) – un chemin plus rapide vers des gains d’énergie et de performances précieux dans leurs produits. Intel a une longue expérience dans l’introduction des nouvelles technologies les plus critiques de l’industrie, telles que le silicium contraint, la grille métallique Hi-K et le FinFET, pour faire avancer la loi de Moore. Avec l’arrivée de la technologie gate-all-around PowerVia et RibbonFET en 2024, Intel continue de dominer l’industrie en matière de conception de puces et d’innovations de processus.

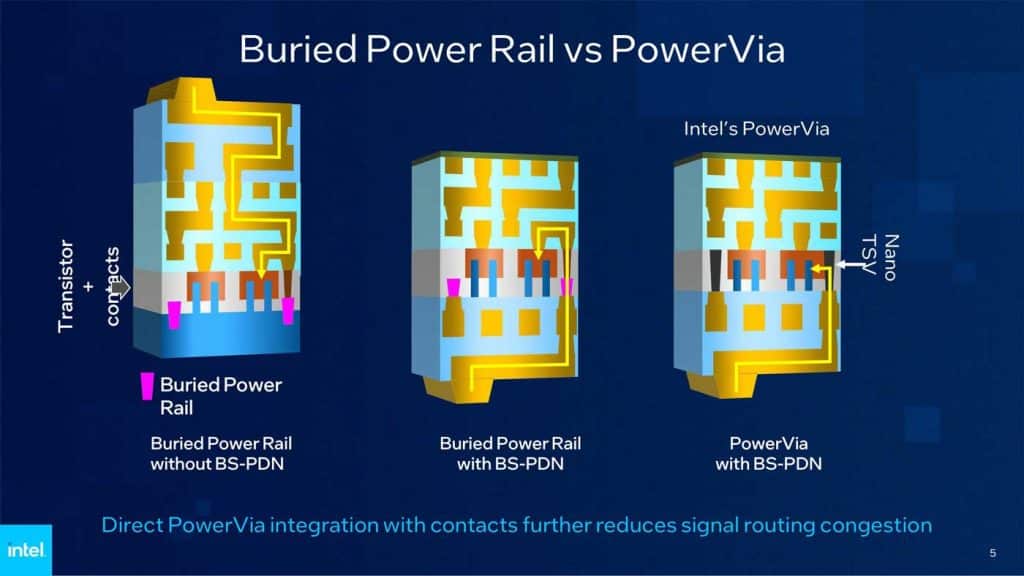

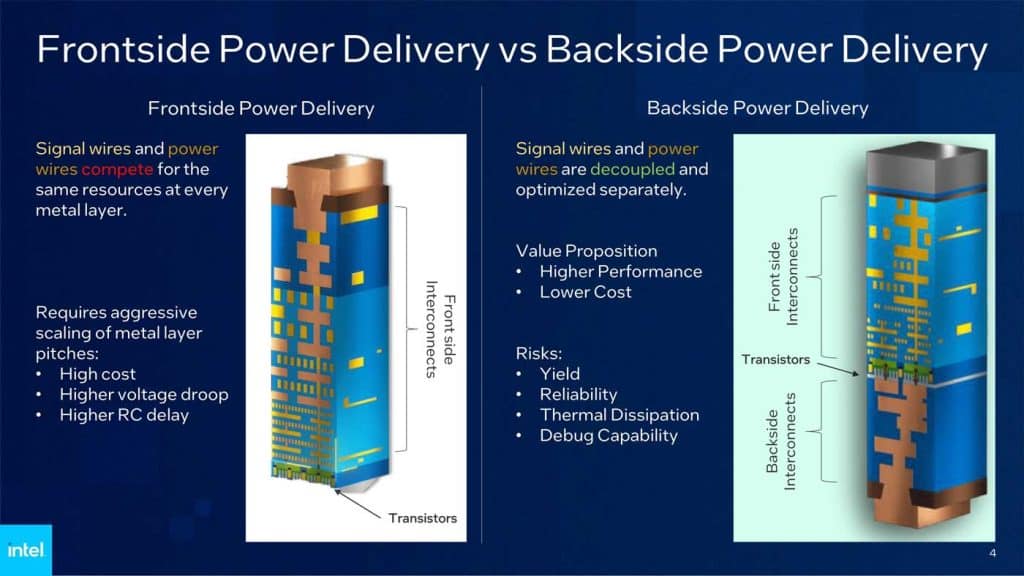

PowerVia est le premier à résoudre le problème croissant de goulot d’étranglement d’interconnexion pour les concepteurs de puces. Les cas d’utilisation en plein essor, y compris l’intelligence artificielle et les graphiques, nécessitent des transistors plus petits, plus denses et plus puissants pour répondre aux demandes informatiques toujours croissantes. Aujourd’hui et au cours des dernières décennies, les lignes d’alimentation et de signal dans l’architecture d’un transistor se sont disputées les mêmes ressources. En séparant les deux, les puces peuvent augmenter les performances et l’efficacité énergétique, et offrir de meilleurs résultats aux clients. La fourniture d’alimentation par l’arrière est essentielle à la mise à l’échelle des transistors, permettant aux concepteurs de puces d’augmenter la densité des transistors sans sacrifier les ressources pour fournir plus de puissance et de performances que jamais.

En dissociant le développement de PowerVia de RibbonFET, Intel pourrait relever ces défis rapidement pour assurer la préparation à la mise en œuvre dans le silicium basé sur les nœuds de processus 20A et 18A d’Intel. Les ingénieurs d’Intel ont développé des techniques d’atténuation pour empêcher les thermiques de devenir un problème. La communauté de débogage a également développé de nouvelles techniques pour garantir que la nouvelle structure de conception puisse être correctement déboguée. En conséquence, la mise en œuvre du test a fourni des mesures de rendement et de fiabilité solides tout en démontrant la proposition de valeur intrinsèque de la technologie bien avant qu’elle ne rejoigne la nouvelle architecture RibbonFET.

Le test a également tiré parti des règles de conception activées par la lithographie EUV (ultraviolet extrême), qui a produit des résultats, notamment une utilisation standard des cellules de plus de 90 % sur de grandes surfaces de la matrice permettant une plus grande densité de cellules, ce qui devrait réduire les coûts. Le test a également montré une amélioration de plus de 30 % de la chute de tension de la plate-forme et un avantage de fréquence de 6 %. Intel a également obtenu des caractéristiques thermiques dans la puce de test PowerVia conformes aux densités de puissance plus élevées attendues de la mise à l’échelle logique.

Et ensuite : Dans un troisième article qui sera présenté lors du VLSI, le technologue Intel Mauro Kobrinsky expliquera les recherches d’Intel sur des méthodes plus avancées pour déployer PowerVia, telles que l’activation à la fois de la signalisation et de l’alimentation électrique à l’avant ou à l’arrière de la plaquette.

Apporter PowerVia aux clients en avance sur l’industrie et continuer à innover dans le futur est conforme à la longue histoire d’Intel d’être le premier à commercialiser de nouvelles innovations en matière de semi-conducteurs tout en innovant constamment.