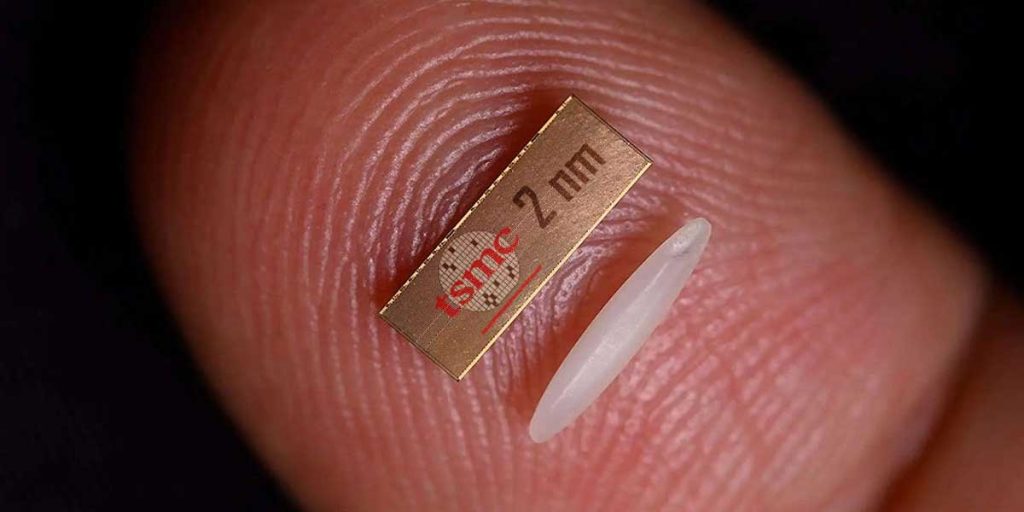

L’industrie des semi-conducteurs est confrontée à plusieurs défis diversifiés. Tout d’abord, il faut passer au BSPDN, c’est-à-dire acheminer l’énergie par l’arrière de chaque transistor. Ensuite, nous devons réduire leur taille tout en maintenant le même rapport puissance/rendement et en augmentant la densité. Enfin, tout cela doit rester rentable et économique. Les deux premiers problèmes ont déjà été résolus et les premières phases de mise en œuvre sont en cours. Dans seulement deux ans, nous verrons ces avancées sur les PC et les serveurs du monde entier. Cependant, le troisième problème demande plus de temps et d’ici 2025, les processeurs à 2 nm coûteront environ 61 % de plus.

Les processeurs n’ont pas fini de coûter toujours plus cher

La réponse n’est pas aussi simple qu’elle en a l’air, nous ne parlons pas de l’augmentation du coût des galettes de silicium (qui est déjà en cours). En fait, il s’agit plutôt du coût du processus de conception avancée, depuis la phase de conception initiale jusqu’à la finalisation du circuit intégré. Une étude a analysé l’évolution ainsi que les coûts et les résultats sont inquiétants.

Il est important de ne pas se méprendre sur cette affirmation. La comparaison est saisissante si l’on considère les 15 dernières années, de 2010 aux prévisions de 2025, c’est-à-dire la transition des 28 nm aux 2 nm. L’étude, menée par International Business Strategies (IBS), a pris en compte les données par lithographie plutôt que par année, en combinant les coûts des sept principales étapes de conception pour chaque nœud de fabrication, fournissant ainsi une estimation assez précise du coût total.

En 2010, les 28 nm étaient tellement abordables que nous en ririons aujourd’hui, avec un coût total de seulement 48 millions de dollars. Le passage aux 22 nm a ensuite entraîné une augmentation de 31,25 %, soit un coût total de 63 millions de dollars.

Ensuite, les 16 nm sont venus avec un coût total estimé à 90 millions de dollars, et comme prévu, le pourcentage d’augmentation des coûts a atteint 42,85 %. À partir de là, les coûts ont connu des fluctuations considérables. Entre les 16 nm et les 7 nm, il y a eu quelques étapes intermédiaires, telles que les 14 nm, les 10 nm, ou encore les 8 nm de Samsung, mais elles ne sont pas significatives dans les données.

De 16 nm à 7 nm, les coûts sont passés de 90 millions à 249 millions de dollars, principalement en raison de l’adoption de la lithographie EUV. Cela représente une augmentation de 76,66 %.

Passons maintenant au saut logique des 7 nm aux 5 nm, qui a fait grimper les coûts de 249 millions à 449 millions de dollars, soit une augmentation de 80,32 %. Apple a déjà lancé les puces 3 nm, et dans un peu plus d’une semaine, l’iPhone 15 équipé de la puce A17 Bionic sera disponible à la vente. La conception de ces puces M3 a nécessité une augmentation de 29,39 % par rapport aux 5 nm.

Enfin, il reste à faire le saut des 3 nm, actuellement à la pointe de la technologie, aux nouveaux processeurs à 2 nm qui seront disponibles chez TSMC, Samsung et Intel en 2025, mais à un coût plus élevé. Le coût passera ainsi de 581 millions à 725 millions de dollars pour la conception de ces puces. Cela signifie que tous les concepteurs devront dépenser 24,78 % de plus, et par rapport aux processeurs 5 nm actuels, cela représente une augmentation de plus de 61 % en à peine deux ans.

En présentant ces chiffres, nous pouvons constater que les sept étapes suivantes ont été prises en compte par l’équipe d’IBS :

- Qualification de la propriété intellectuelle.

- Conception architecturale.

- Vérification de la conception.

- Conception physique des puces.

- Développement de logiciels associés.

- Création de prototypes.

- Validation finale.

Bref, les coûts continuent d’augmenter et bien que les marges restent stables grâce à la création de plus de puces par galette de silicium, ce qui réduit le coût par puce, cette économie n’est réalisable que si le taux de succès dépasse les 80 % pour chaque galette.

Il y a environ six mois, nous avons constaté que tous les concepteurs utilisent de plus en plus des techniques d’intelligence artificielle avancées pour la disposition, le câblage et l’agencement des éléments clés, tels que la SRAM. Les aspects logiques sont également assistés par des IA, principalement développées par des entreprises comme Synopsys, Cadence et Ansys. Ces trois entreprises sont leaders dans ce domaine crucial en tant qu’outils et elles seules peuvent éviter que les processeurs à 2 nm ne coûtent encore plus cher.

Il s’agira d’un investissement initial qui se rentabilisera rapidement, tout en permettant de gagner beaucoup de temps pour les ingénieurs. Il reste à voir si les coûts pourront continuer à diminuer à chaque étape de la lithographie, ou si nous approchons du moment où cela deviendra insoutenable, en particulier lorsque nous nous rapprocherons du transistor atomique, une notion qui relevait encore de la science-fiction il y a seulement une décennie.